PCIe之ASPM及子状态(L0s L1)简介

PCIe之ASPM及子状态(L0s L1)简介

ASPM(Active State Power Management,主动状态电源管理) 是 PCI Express(PCIe)规范中用于在设备处于 工作状态(D0) 时动态降低链路功耗的关键机制。它通过控制物理链路的低功耗状态,无需将设备完全挂起到深度睡眠(如 D3),从而在保持功能可用性的同时节省电能。

ASPM 定义了多个链路级低功耗子状态,主要包括:

- L0s

- L1(基础状态,也称 L1.0)

- L1.1

- L1.2

下面对这四种状态进行简单介绍。

一、总体架构:ASPM 的层次关系

| 状态 | 类型 | 是否需两端协商 | 典型延迟 | 功耗节省 |

|---|---|---|---|---|

| L0 | 正常活动 | — | 0 | 无 |

| L0s | 轻度节能 | ❌ 单端可进 | ~10–100 ns | 低 |

| L1.0 | 中度节能 | ✅ 必须两端同意 | ~1–2 μs | 中 |

| L1.1 | 深度节能 | ✅ + CLKREQ# | ~2–10 μs | 高 |

| L1.2 | 极致节能 | ✅ + CLKREQ# | ~50–200 μs | 极高 |

✅ 所有状态都发生在 设备处于 D0(运行状态) 时,与系统睡眠状态(S0/S3)无关。

二、逐状态简介

1. L0s(Low Power State with Short Latency)

✅ 核心特点:

- 延迟极低(纳秒级),对性能几乎无影响。

- 仅关闭发送器(Tx),接收器(Rx)通常保持监听。

- 单向进入:链路一端可独立进入 L0s,无需对方同意。

- 适用于高频、突发性通信场景(如 NVMe SSD、网卡)。

🔧 工作机制:

- 空闲时,Tx 关闭,进入“电气空闲”(Electrical Idle)。

- 退出时,发送 EIOS(Electrical Idle Exit Ordered Set) 通知对端。

- 无需重新训练链路(Link Training)。

⚠️ 局限:

- 节能效果有限(仅省 Tx 功耗)。

- 某些旧设备或服务器平台会禁用 L0s,因可能引入微小延迟抖动。

2. L1(即 L1.0,基础 L1 状态)

✅ 核心特点:

- 需两端协商:通过 DLLP(Data Link Layer Packet)交换

PM_Enter_L1和PM_Ack_L1。 - 关闭 Tx 和 Rx,但主参考时钟(RefClk)保持运行。

- 延迟在 1–2 微秒 量级。

- 节能效果明显,广泛用于桌面和服务器。

🔧 工作机制:

- 双方确认空闲后,进入 L1。

- 退出时需重新同步链路(但无需完整 Link Training)。

- 时钟持续运行,确保快速唤醒。

📌 注意:

- L1.0 是 PCIe 1.0 就定义的状态,兼容性最好。

- 大多数 BIOS 默认启用 “L0s + L1” 组合。

3. L1.1(Enhanced L1 Substate)

✅ 引入背景:

- PCIe 2.0 新增,为移动设备进一步降低功耗。

- 核心改进:允许关闭主参考时钟(RefClk)。

🔑 关键机制:CLKREQ# 信号

- CLKREQ# 是一个边带信号(通常为开漏、低有效)。

- 当设备在 L1.1 中需要唤醒时,**拉低 CLKREQ#**。

- 上游设备(如 Root Complex)检测到后,重新开启 RefClk。

- 时钟稳定后,链路退出 L1.1。

✅ 优势:

- 比 L1.0 多节省 10–30% 功耗(时钟树是主要功耗源之一)。

- 延迟仍可控(通常 <10 μs)。

⚠️ 要求:

- 必须有 CLKREQ# 引脚连接(硬件设计支持)。

- 链路两端均需支持 L1.1(通过 PCIe Capability 寄存器通告)。

4. L1.2(Deeper L1 Substate)

✅ 核心特点:

- 在 L1.1 基础上更进一步:完全关闭主时钟域。

- 使用极低频辅助时钟(如 100 kHz)监听 CLKREQ# 或唤醒事件。

- 功耗最低,适用于 Wi-Fi、蓝牙、传感器 等低频外设。

🔧 工作机制:

- 主 RefClk 完全关闭。

- PHY 使用低功耗振荡器维持最小监听能力。

- 唤醒流程:

拉低 CLKREQ# → 开启 RefClk → 时钟稳定 → 退出 L1.2 → 恢复通信

⏱️ 延迟代价:

- 退出延迟显著增加,典型值 50–200 μs,甚至更高。

- 不适用于延迟敏感场景(如实时音视频、高性能存储)。

✅ 节能效果:

- 可比 L1.0 节省 50% 以上链路功耗。

- 在笔记本待机时对延长续航有显著贡献。

三、四种状态对比总表

| 特性 | L0s | L1.0 | L1.1 | L1.2 |

|---|---|---|---|---|

| 引入版本 | PCIe 1.0 | PCIe 1.0 | PCIe 2.0 | PCIe 2.0 |

| 进入是否需协商 | ❌ 否 | ✅ 是 | ✅ 是 + CLKREQ# 支持 | ✅ 是 + CLKREQ# 支持 |

| 主参考时钟(RefClk) | 保持开启 | 保持开启 | 可关闭 | 完全关闭 |

| 是否需要 CLKREQ# | ❌ 否 | ❌ 否 | ✅ 是 | ✅ 是 |

| 典型退出延迟 | 10–100 ns | 1–2 μs | 2–10 μs | 50–200 μs |

| 功耗节省程度 | 低 | 中 | 高 | 极高 |

| 典型应用场景 | 高速 NVMe、网卡 | 通用设备 | 笔记本内嵌设备 | 蓝牙/Wi-Fi/传感器 |

| 链路训练(LTSSM) | 无需 | 轻量同步 | 需时钟恢复 + 同步 | 完整时钟恢复 + 同步 |

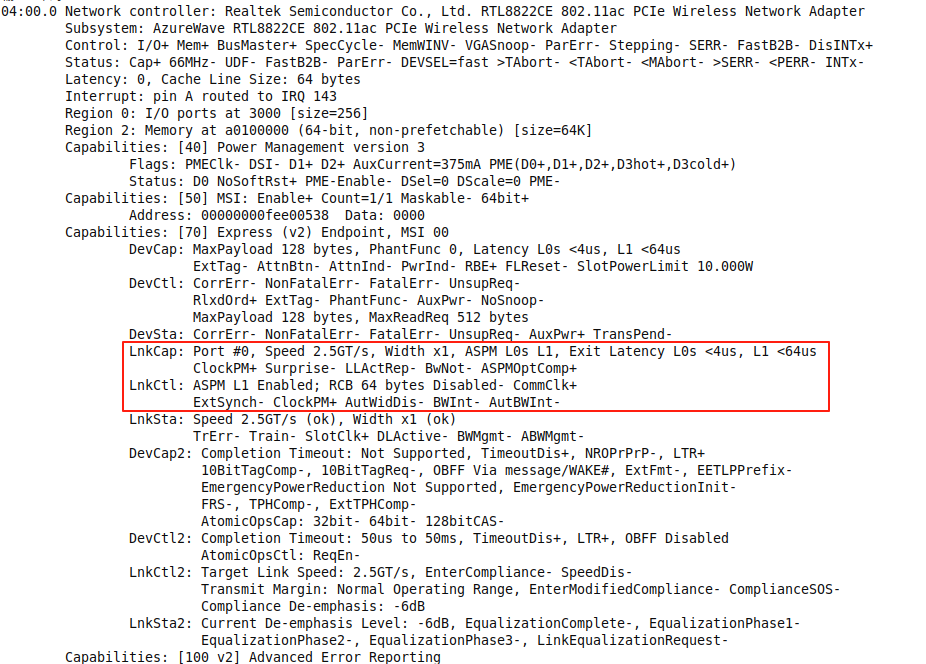

四、系统中的配置(Linux 示例)

# 查看当前 ASPM 策略

cat /sys/module/pcie_aspm/parameters/policy

# 输出:default, performance, powersave, powersupersave

# 强制启用 ASPM(需内核支持)

echo powersupersave > /sys/module/pcie_aspm/parameters/policy查看某设备的ASPM子状态:

sudo lspci -vv -s 04:00.0输出类似如下:

五、总结

- L0s:快进快出,省一点点,适合高性能设备。

- L1.0:基础节能,平衡延迟与功耗,通用性强。

- L1.1:关时钟,靠 CLKREQ# 唤醒,移动设备主力。

- L1.2:极致省电,牺牲延迟,适合低频外设。

🎯 设计建议:

- 服务器/工作站:禁用 ASPM 或仅用 L0s(保性能)

- 笔记本/移动设备:启用 L1.1/L1.2(保续航)

- 嵌入式/IoT:优先 L1.2(极致低功耗)

如需权威参考,请查阅: 《PCI Express Base Specification》Rev 5.0 或 6.0

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 DD'Notes!

评论